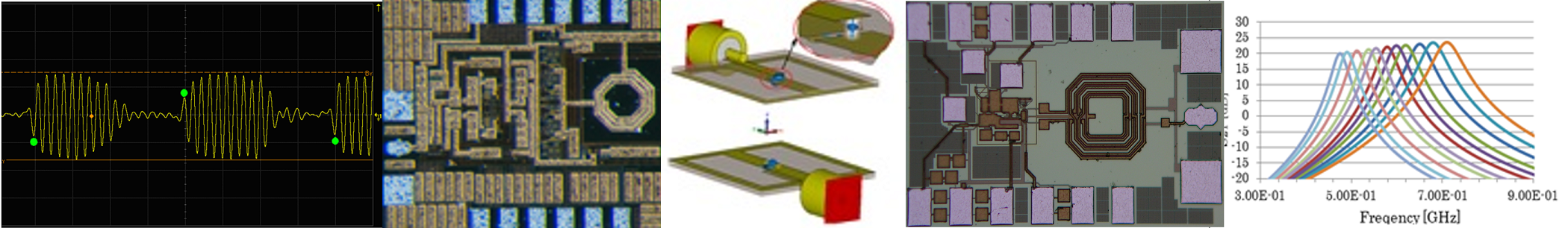

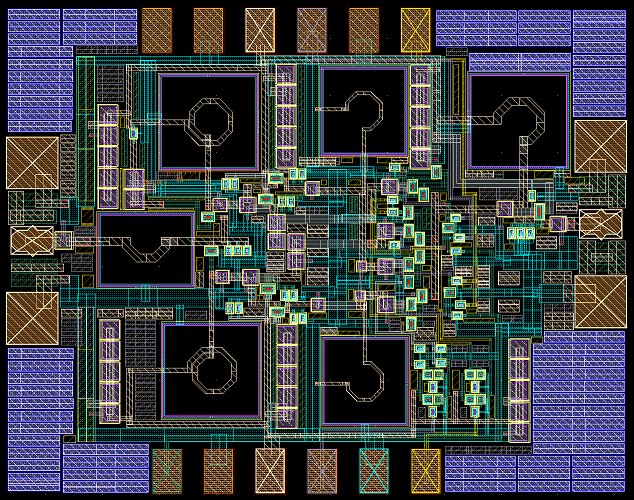

現在の無線端末(送受信機)のアナログフロントエンドはおもに低雑音増器(Low Noise Amplifier)、電力増幅器(Power Amplifier)、ミキサ、フィルタ、VCO(Voltage Controlled Oscillator)、それに安定した局部発振周波数を実現するためのPLL(Phase Locked Loop)というブロックで構成されている。また、近年の無線通信機器は 小型化が求められているのに対してそのサービス内容はますます複雑化している。この流れによりアナログフロントエンドをCMOS (Complementary Metal Oxide Semiconductor)プロセスで実現することによりディジタル回路との混載が可能になりRFフロントエンドからベースバンド部,更にはディジタル信号処理部までを含めたモ ジュールをワンチップで構成することも可能になった。他にも、CMOSプロセスを用いることにより高速データ転送、低ノイズ、高線形性および低消費電力を必要とするア プリケーションにピーク性能を提供するという利点がある。

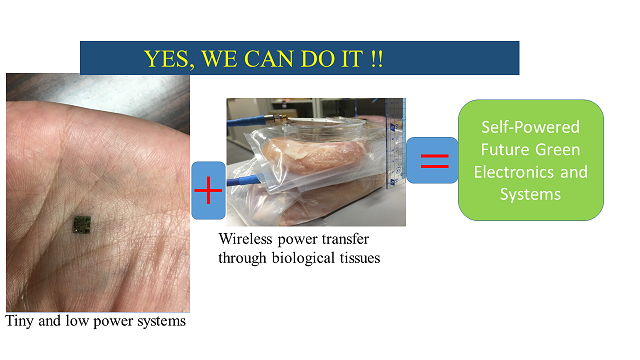

それに加え、IoT(Internet of Things)等の発達により無線通信の通信量は年々増大しており、 全二重通信やアレーアンテナでのビームフォーミング等の大容量化技術が注目されている。 これらを実現するためのハードウェア技術として、CMOSプロセスを用いたフロントエンドを開発している。 第5世代移動通信向けの準ミリ波帯CMOSプロセスでの集積化を目指している。